Контролепридатність схем в FPGA-проектах за ознакою розсіюваної потужності

Анотація

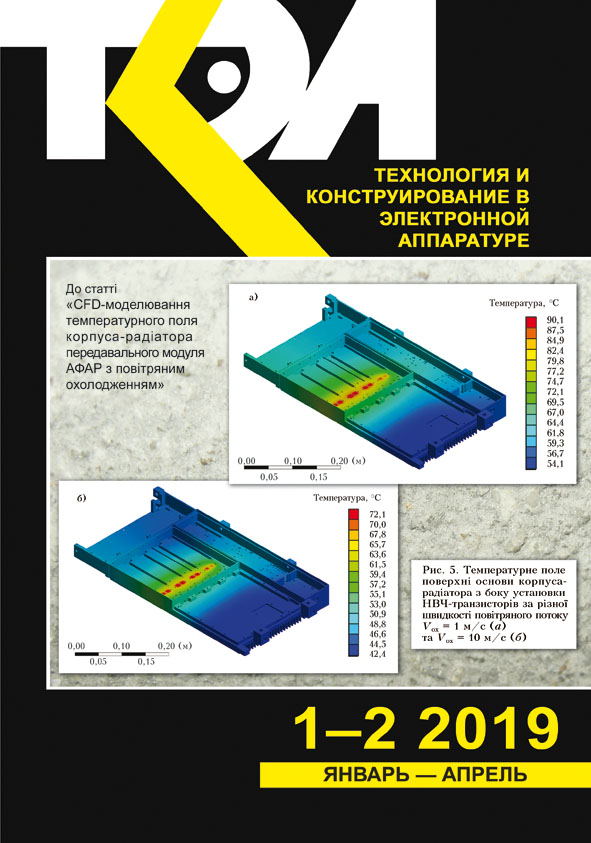

Розглядаються питання контролепридатності схем FPGA-проектів. Аналізується логічна контролепридатність та її різновиди: структурна і структурно-функціональна. Відзначаються особливості систем критичного застосування, функціонування яких поділяється на два режими — нормаль¬ний та аварійний, в яких на входи цифрових схем компонентів подаються різні вхідні дані, що обумовлює розширення структурно-функціональної контролепридатності до дворежимної. Відмічається створення проблеми виявлення прихованих несправностей, які можуть накопичуватися в нормальному режимі та проявлятися в аварійному. Відзначаються особливості контролепридатності схем в FPGA проектах і її переваги, важливі для критичних додатків. Аналізуються обмеження логічної контролепридатності схем, а також можливість і доцільність розширення традиційно використовуваної логічної форми до контролепридатності за ознакою енергоспоживання. Визначається контролепридатність схем в FPGA- проектах за енергоспоживанням та ії різновиди: нижня та верхня. Нижня контролепридатність важли¬ва для виявлення несправностей, що призводять до зниження енергоспоживання, наприклад в ланцюгах загальних сигналів, таких як скидання або синхронізація. Верхня важлива для виявлення несправностей, що підвищують рівень енергоспоживання, наприклад короткі замикання. Визначаються можливості оцінки контролепридатності за енергоспоживанням FPGA-проектів за показниками розсіюваної або споживаної потужності та вказується доцільність розвитку верхньої контролепридатності за розсіюваною потужністю. Зазначаються особливості моніторингу розсіюваної потужності для FPGA- проектів. Пропонується аналітична оцінка придатності схем для діагностування несправностей, що підвищують розсіювану потужність, таких як коротке замикання, і організація моніторингу її переви¬щення. Проводяться експерименти в САПР Quartus Prime Lite по оцінці верхньої контролепридатності за розсіюваною потужністю масштабованих схем регістрів зсуву, що реалізовані в FPGA-проектах на базі вбудованого IP-Core, та користувацького VHDL-опису. Наводяться результати експериментів, що оцінюють залежність рівня контролепридатності від площі, що займає схема на кристалі FPGA.

Посилання

Abramovici M., Breuer M., Friedman A. Digital Systems Testing and Testable Design. New York: Wiley-IEEE Press, 1990, 652 p.

Matrosova A., Nikolaeva E., Kudin D., Singh V. PDF testability of the circuits derived by special covering ROBDDs with gates. IEEE East-West Design and Test Symposium (EWDTS 2013), Russia, Rostov-on-Don, 2013, pp. 1–5.

Nicolaidis M., Zorian Y., Pradhan D. On-Line Testing for VLSI. Journal of Electronic Test-ing: Theory and Application, 1998, Vol. 12, № 1/2, pp. 7–159.

Metra C., Schiano L., Favalli M., Ricco B. Self-Checking scheme for the on-line testing of power supply noise. Proc. of the Design, Automation and Test in Europe Conference, France, Paris, 2002, pp. 832–836.

IEC 61508-1:2010. Functional safety of electrical/electronic/programmable electronic safety related systems. Part 1: General requirements.

Andrashov A., Kharchenko V., Siora A., Sklyar V., Volkoviy A. A Certification of FPGA-based safety Instrumentation and Control platform in accordance with IEC 61508. Critical Infra-structure Safety and Security, 2011, Vol. 1, pp. 148–152.

Drozd M., Drozd A. Safety-Related Instrumentation and Control Systems and a Problem of the Hidden Faults. The 10th International Conference on Digital Technologies, Slovak Republic, Zhilina, 2014, http://dx.doi.org/10.1109/DT.2014.6868692

Abramovich M., Stroud C., Hamilton C., Wijesuriya S., Verma V. Using roving STARs for on-line testing and diagnosis of FPGAs in fault-tolerant applications. IEEE International Test Conference, USA, Atlantic City, 1999, pp. 973–982.

Gillis D. The Apocalypses that Might Have Been. URL: https://www.damninteresting.com/the-apocalypses-that-might-have-been

Final Report on the August 14, 2003 Blackout in the United States and Canada: Causes and Recommendations. U.S.-Canada Power System Outage Task Force, USA, 2004, URL: https://www3.epa.gov/region1/npdes/merrimack-station/pdfs/ar/AR-1165.pdf

Drozd A., Kharchenko V., Antoshchuk S., Sulima J., Drozd M. Checkability of the digital components in safety-critical systems: problems and solutions. IEEE East-West Design & Test Symposium, Ukraine, Sevastopol, 2011, http://dx.doi.org/10.1109/EWDTS.2011.6116606

Drozd A., Drozd J., Antoshchuk S., Antonyuk V., Zashcholkin K., Drozd M., Titomir O. Green Experiments with FPGA. In book: Green IT Engineering: Components, Networks and Sys-tems Implementation. Vol. 105 / Ed. By V. Kharchenko, Y. Kondratenko, J. Kacprzyk, Berlin, Hei-delberg: Springer International Publishing, 2017, pp. 219–239, http://dx.doi.org/10.1007/978-3-319-55595-9_11

Kharchenko V. S. FPGA-based NPP I&C Systems: Development and Safety Assessment. Ed. by V. S. Kharchenko, V. V. Sklyar, Ukraine, Kharkiv: RPC Radiy, National Aerospace University “KhAI”, SSTC on Nuclear and Radiation Safety, 2008, 188 p.

Intel Quartus Prime Standard Edition User Guide: Getting Started. URL: https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/ug/ug-qps-getting-started.pdf

Intel Quartus Prime Standard Edition User Guide: Power Analysis and Optimization (2018). URL: https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/ug/ug-qps-power.pdf

Antoniuk V.V., Drozd О.V., Nikolenko I.М. Hardware model of digital components of computer systems. Refrigeration Engineering and Technology, 2013, №2 (142), pp. 81 – 83. (Ukr)

Pat. 102743 of Ukraine. N-bit binary codes sequence generator / O.V. Drozd, et al., 2013, bul. № 15. (Ukr)

Авторське право (c) 2019 Антонюк В. В., Дрозд О. В., Дрозд Ю. В., Степова Г. С.

Ця робота ліцензується відповідно до Creative Commons Attribution 4.0 International License.